便攜式RFID讀寫器的設計與實現

文章出處:http://5052h112.com 作者:高天寶等 人氣: 發表時間:2011年10月14日

射頻識別(RFlD)技術是一種非接觸式的自動識別技術,其基本原理是利用射頻信號及其空間耦合和傳輸特性,實現對靜止或移動物體的自動識別。一個射頻識別系統一般包括射頻標簽、讀寫器以及主機等幾個部分。目前國內應用于超高頻的RFID讀寫器較少,而且整機價格昂貴、體積龐大、需外接天線或天線陣列、不便于攜帶且多不能單機工作。本設計的目的在于以盡可能低的硬件成本實現一種基于ISO/IEC 18000—6B標準的便攜式RFID讀寫器,并可通過軟件升級后支持其他標準或多標準。

1、理論分析理

RFID系統工作時,首先由讀寫器發射一個特定的一步的處理。詢問信號,當射頻標簽感應到這個信號后,就會給出相2讀寫器硬件設計應的應答信號;讀寫器接收這個應答信號并對其進行處理,返回給外部主機或進行相應操作。

本文所實現的讀寫器包含射頻收發模塊和數字基帶處理模塊,其中射頻收發模塊又包括射頻發射機和射頻接收機兩部分,總體結構如圖1所示。系統在工作時首先由數字基帶處理模塊產生需要向射頻標簽發送的詢問信號,然后由射頻發射機將這個信號轉換成為射頻信號發射出去。

圖1讀寫器總體結構

射頻標簽接收到這個信號后,會給出相應的應答信號,回波信號。這個回波信號將由射頻接收機接收并進行處理,轉換成為數字信號后送給數字基帶模塊進行進一步處理。

2、讀寫器硬件設計

如前所述,本讀寫器的硬件主要包括射頻收發機模理,返回給外部主機或進行相應操作。塊和數字基帶處理模塊,其中射頻收發機模塊包括射頻發射機和射頻接收機,總體結構如圖1所示。在系統結構的選擇上,本讀寫器以降低成本為主要目標,射頻發射機和射頻接收機采用了零中頻結構,在很大程度上減少了所需的器件;數字基帶處理模塊采用了以單片機為主的結構,而沒有采用高速的DSP,也節省了一定的成本。

2.1射頻發射機

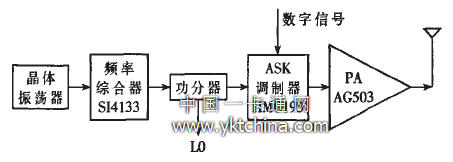

發射機電路主要包括晶體振蕩器、頻率綜合器、功分器、ASK調制器、功率放大器(PA)以及發射天線等,其主體結構如圖2所示。

圖2射頻發射機結構框圖

本設計中,頻率綜合器采用了集成芯片S14133,這是一款可編程的鎖相環芯片,可以通過數字編程控制其輸出頻率。正是通過這一性能,實現了系統在860MHz一960MHz的頻率范圍內的跳頻操作,從而避免頻帶內其他信號的干擾。由S14133輸出的射頻載波經過一個功分器后,一路送往接收機作為本地振蕩信號LO,另一路則送至ASK調制器。這里的ASK調制器采用了一款結構非常簡單的芯片HMCl95,它可以簡化為一個高速開關,由需要發送的數字信號控制其通斷,以此完成對載波的調制。經調制的載波由功率放大器放大,最后送至天線發射出去。

鑒于實際工作的需要,這里并沒有采用高性能的功率放大器,而是采用了一個價格低廉的緩沖放大器芯片AG503,其輸出功率最高可達17dBm,即O.05W。發射天線也采用了極為簡單的PCB印制偶極子天線,無需外接。此時讀寫器的工作距離可達80cm。由于載波在近距離的自由空間的衰減與傳播距離的平方近似于成正比,故可以計算當發射機的等效發射功率(EIRP)達到36dBm,即4W時,讀寫器的工作距離可以達到7m。

2.2射頻接收機

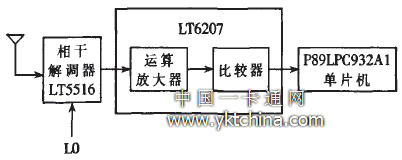

接收機電路主要包括相干解調器、運算放大器、比較器等,其主體結構如圖3所示。相干解凋器采用I、Q正交解調。接收機的設計難點主要為同頻接收。因為對于無源標簽,在循環發送詢問信號期間,讀寫器需要始終發送載波信號來給標簽提供能量。

圖3射頻接收機結構框圖

然而,從發射機到接收機的隔離一般在20dB以下,因此在接收機接收標簽應答信號的同時也會接收到這個比較強的載波信號,這就要求接收機必須具有很高的線性度。對于這個問題,既不能像手機系統中那樣采用雙頻收發,也不能像有些射頻收發機那樣采用分時收發,而只能通過提高接收機的線性度和增大發射機與接收機之間的隔離來解決。

本接收機中采用了一個高線性度低噪聲的直接轉換正交解調器LT5516,它的ldB壓縮點可達6.6dBm,而噪聲系數只有11.4dB。由于一般的低噪聲放大器(LNA)的線性度不能滿足要求,故在前端沒有采用低噪聲放大器。LT5516的RF輸入端口與LO輸入端口均采用差分輸入,故在它的兩個輸入端口處各接了一個平衡,不平衡變換器Balun(圖中未示出)。由于L1'5516的兩個輸入端口的輸入阻抗為2001"l,而外部的RF與Lo輸入信號均是匹配在50Ω,故本設計中的Balun采用的是1:4的變壓器,實現從單端信號到差分信號轉換的同時也實現了從50Ω到200Ω的阻抗變換。

LT5516的輸出是正交的I,Q兩路信號,并且分別以差分形式輸出。它的輸出阻抗為60Ω,在輸出端接了270pF的對地電容:從而獲得截止頻率位于10MHz的RC低通濾波器,以此濾出高頻分量。

運算放大器和比較器采用了噪聲較低的LT6207,它含有4個運算放大器,將其中兩個作為第一級,另兩個作為第二級。LT5516的輸出差分信號經過低通濾波,采用交流耦合到第一級運算放大器的輸入端,經放大后輸出單端信號,然后再經直流耦合到第二級運算放大器的反相輸入端。第二級運算放大器采用開環結構,實現電壓比較器的功能,其同相輸入端接比較電平。這樣在第二級的輸出端便可以得到數字信號,這就是射頻接收機處理之后的信號。該信號將被送至數字基帶處理模塊進行進一步處理。

2.3數字基帶處理模塊

數字基帶處理模塊主要包括一個單片機、兩個轉換芯片、外部接口以及蜂鳴器等,其主體結構如圖4所示。單片機采用了Philips的P89LPC932A1單片機,外部時鐘頻率為12MHz。整個系統的控制信號,如射頻收發機中頻率綜合器的初始化信號、使能信號、跳頻指令信號、相干解調器的使能信號以及ASK調制器的數字輸入信號等均由這個單片機提供。另外,標簽的應答信號經射頻接收機接收處理后也需送至單片機進行解碼、校驗,然后由單片機作出判斷,給出相應的卡號等信息。數字基帶處理模塊與讀寫器外部的接口包括RS232串口和USB端口,這里采用了兩個轉換芯片MAX3232和PL2303.分別實現從單片機到相應接口的信號轉換,以此完成讀寫器與外部主機的通信。這樣既可以由外部主機對讀寫器進行控制,也可以由讀寫器將讀取的標簽信息返回給外部主機。(未完)

全文下載:http://www.yktchina.com/bbs/Read-b4-t6329.htm

(清華大學微電子學研究所 高天寶,王敬超,張春,李永明,王志華)