智能卡控制器IP核的設計與實現

文章出處:http://5052h112.com 作者: 人氣: 發表時間:2012年03月07日

摘要:本文介紹了一款兼容ISO7816-3協議的智能卡控制器IP核。該IP核能實現對智能卡的探測、電源管理、復位和讀寫控制等功能。文章側重于介紹智能卡控制器采用Verilog語言實現數字邏輯的方法。

關鍵詞:ASIC;ISO7816;智能卡;IP核;Verilog 語言

1、引言

隨著信息技術的飛速發展,越來越多的地方要求對用戶身份的識別以及重要數據的安全存儲。而智能卡(SmartCard)又稱集成電路卡(Integrated Circuit Card 即IC卡),是具有高的可靠性安全性和靈活性的數據承載設備,現已被廣泛應用于政府、金融、電信、交通及公共事業等領域。

智能卡控制器是連接智能卡和主控設備的橋梁,由于智能卡的應用不斷增加,越來越多的SOC芯片內嵌了智能卡控制器IP核。這種基于IP核的設計方式已成為IC設計的主流,這里主要介紹智能卡控制器IP核的數字邏輯實現方法以及其在硬盤加密芯片中的應用。

2、協議簡介

這里僅對本文中要用到的部分協議內容作簡要說明,詳細的協議內容請見參考文獻1。

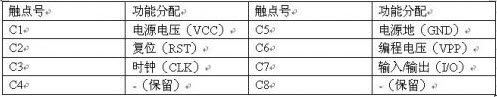

智能卡共有八個觸點,其中有用的就C1、C2、C3、C5、C6、和C7六個觸點,具體見下表:

表1:智能卡觸點

智能卡控制器是通過智能卡觸點C7(I/O)與控制器進行半雙工串行通信的,在每一時刻觸點C7只有狀態Z和狀態A兩種狀態。

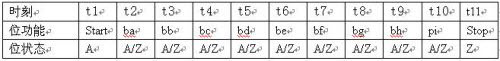

智能卡要傳輸一個字節(8個Bit)數據的要11個Bit位的時間寬度,在下表中被記成t1到t11。其中第一個時刻t1傳輸的Start位被稱為起始位;第二到第九個時刻,即時刻t2到時刻t9,傳輸的數據ba到bh為一個字節的八個位;時刻t10傳送的pi位為奇偶校驗位;最后一個時刻t11傳輸的Stop位被稱為停止位,標志著一個字節(8個Bit)的數據傳輸完成。請見下表:

表2:智能卡串行傳輸數據格式

3、微體系結構

3.1、接口信號

該IP核接口主要分為CPU總線接口、中斷信號和智能卡控制接口,這里主要介紹一下有關智能卡控制的接口信號,即連接或控制智能卡上有效觸點的信號,它們為:

1) 智能卡是否存在信號IC_PRES:用于探測智能卡座上是否有智能卡存在,當有智能卡插入或拔出時,該信號的電平發生跳變,本IP核能夠探測該信號的電平的變化,并以中斷等方式報告給CPU;

2) 智能卡電源控制信號IC_PWR:用于控制智能卡的電源VCC或VPP(觸點C1或C6),用于打開和關閉智能卡電源;

3) 時鐘信號IC_CLK:同智能卡觸點C3相連接,用于向智能卡輸入一定頻率的時鐘信號;

4) 復位信號IC_RST:同智能卡觸點C2相連接,用于向智能卡發出復位信號;

5) 雙向串行數據信號IC_IO:同智能卡觸點C7相連接,用于實現與智能卡的雙向數據通信。

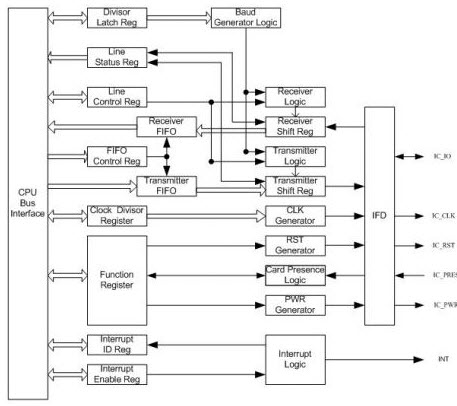

3.2、模塊和功能

智能卡控制器核內部有發送和接收模塊(Transmitter and Receiver)、中斷仲裁模塊(Interrupt Arbitrator)、函數模塊(Function Generator)、時鐘模塊(Clock Generator)、智能卡接口模塊(Interface Device)和訪問寄存器模塊(Register Access Control)六大模塊,這些模塊之間的關系見圖1所示:

圖1 ISO7816智能卡控制器模塊結構圖

主要模塊功能及特征描述如下:

1. 發送和接收模塊:發送和接收模塊負責處理數據幀的發送和接收。發送模塊是將FIFO發送隊列中的數據按照設定的格式把并行數據轉換為串行數據幀,并通過發送端口送出去。接收模塊則監視接收端信號,一旦出現有效開始位,就進行接收,并實現將接收到的異步串行數據幀轉換為并行數據,存入FIFO接收隊列中,同時檢查數據幀格式是否有錯。智能卡控制器的幀結構是通過LCR(Line Control Reg)寄存器設置的,接收和傳送器的狀態被保存在LSR(Line Status Reg)寄存器中。

2. 中斷仲裁模塊:當任何一種中斷條件被滿足時,并且在中斷使能寄存器(IER, Interrupt Enable Reg)中相應位置1,那么智能卡的中斷請求信號INT被置為有效狀態。為了減少和外部軟件的交互,智能卡控制器把中斷分為四個級別,并且在中斷標識寄存器(IIR, Interrupt ID Reg)中標識這些中斷。四個級別的中斷按優先級級別由高到低的順序排列為:智能卡插拔中斷、接收線路狀態中斷、接收數據準備好中斷和傳送擁有寄存器為空中斷;。

3. 函數模塊:該模塊產生智能卡的相關時序。通過向函數寄存器(FR, Function Register)相應的位置入相關的參數來探測智能卡、管理電源和產生復位時序等。

4. 時鐘模塊:時鐘模塊產生相應頻率的時鐘供給智能卡,時鐘的頻率由CPU總線的時鐘頻率和寫入時鐘分頻寄存器(CDR, Clock Divisor Register)的值來決定,關系表達式如下:

fIC_CLK = fCPU /(2 * CDR)

5. 智能卡接口模塊:該模塊將相關信號進行適當的調整,以便適合于IC智能卡的通信。

6. 訪問寄存器模塊:當智能卡控制器被總線控制器選中時,CPU可通過讀或寫操作訪問被地址線選中的寄存器。

4、設計實現

這部分將對本智能卡控制器中主要模塊的數字邏輯的實現方法逐一作簡單說明。

4.1、數據接收模塊

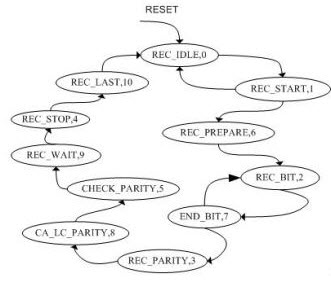

在設計接收模塊的過程中,關鍵是如何實現Receiver Shift的邏輯電路,下圖是本智能卡控制器數據接收模塊中有關Receiver Shift邏輯電路的主控狀態轉換圖:

圖2 接收模塊主控狀機

該狀態機共有十個狀態,其中主要狀態是:狀態1(REC_START)用來探測數據的起始位Start;狀態2(REC_BIT)用來接收數據ba到bh,組成一個字節;狀態3(REC_PARITY)用來接收數據的奇偶校驗位;狀態4(REC_STOP)探測Stop位。

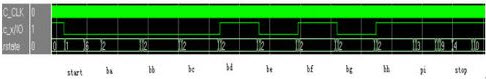

下面是該狀態機控制有關邏輯讀入數據的仿真波形圖:

圖3 接收一個字節數據的狀態變換波形圖

4.2、數據發送模塊

同樣, 對于發送模塊的設計,主要問題也是如何實現Transmitter Shift的邏輯電路,下圖是本智能卡控制器數據發送模塊的主控狀態轉換圖:

圖4 發送模塊主控狀機

該狀態機共有五個狀態:狀態1(SEND_START)用來發送數據的起始位Start;狀態2(SEND_BYTE)用來發送數據ba到bh;狀態3(SEND_PARITY)用來發送數據的奇偶校驗位;狀態4(SEND_STOP)發送Stop位,最后狀態機轉入空閑狀態0(SEND_IDLE)。

下面是該狀態機控制有關邏輯發送數據的仿真波形圖:

圖5發送一個字節數據的狀態變換波形圖

4.3、函數模塊

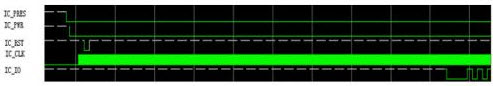

函數模塊可以在軟件控制下產生激活智能卡和關閉智能卡所需的相關時序。這里簡單介紹一下本控制器在軟件的支配下,激活智能卡的過程,見下面的波形圖。

圖6激活智能卡時的波形圖

在該波形圖中,信號IC_PRES首先變低,表明有智能卡插入。接著智能卡控制器通過IC_PWR打開智能卡的電源。待電源穩定后,智能卡控制器通過IC_CLK向智能卡輸出時鐘信號。同樣,在時鐘穩定后,智能卡控制器通過IC_RST向智能卡輸出復位信號。最后智能卡控制器在數據信號IC_IO上探測到智能卡復位應答(ATR,Answer to Reset),這樣就完成了智能卡的激活工作。

5.結論

本方案所設計的智能卡控制器IP核,采用Verilog HDL語言,以較少的硬件代價,在本公司研發的硬盤數據加密芯片中,成功實現了對智能卡密鑰的讀寫控制,并且該方案具有較強的靈活性,可以方便地移植到其它嵌入式應用系統中,具有較高的使用價值。

參考文獻:

[1] GB/T 16649.3-1996 識別卡-帶觸點的集成電路卡-第3部分:電信號和傳輸協議[S].

[2]Donald E, Thomas, Philip R, Moorby. 硬件描述語言Verilog[M] .北京:清華大學出版社,2002:15-261

[3]Neil H.E.Weste, David Harris.CMOS超大規模集成電路設計[M] .北京:中國電力出版社,2006:129-506

[4]沈理.SOC/ASIC設計、驗證和測試方法學[M] .廣州:中山大學出版社,2006:31-202

作者簡介:蘇州市中科集成電路設計中心 章世華 鄒麗麗 董湘麟